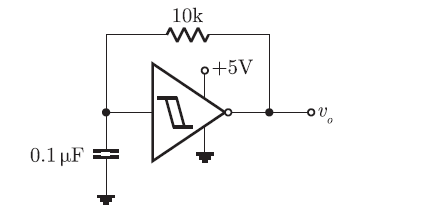

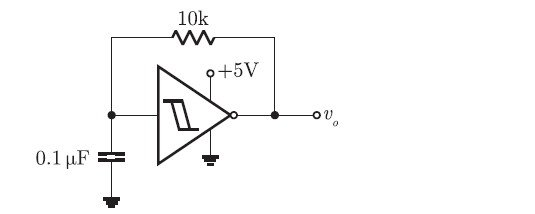

Q. 62 A hysteresis type TTL inverter is used to realize an oscillator in the circuit shown

in the figure.

If the lower and upper trigger level voltages are 0.9 V and 1.7 V, the period (in

ms), for which output is LOW, is _____.

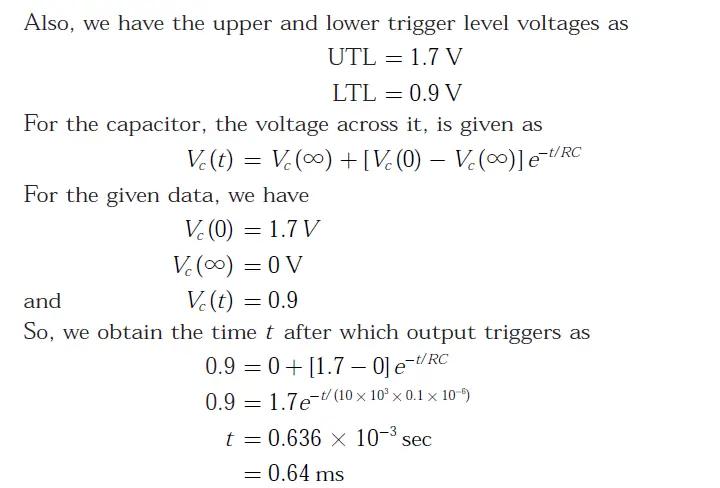

Answer:(0.64 ms)

Explanation:

Excellent