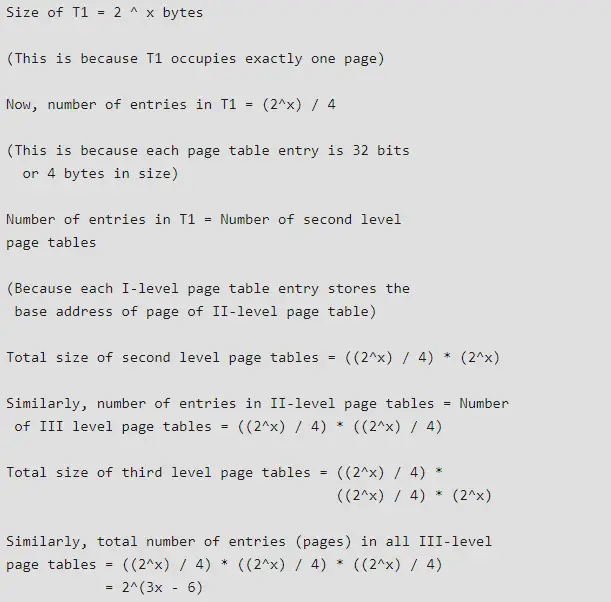

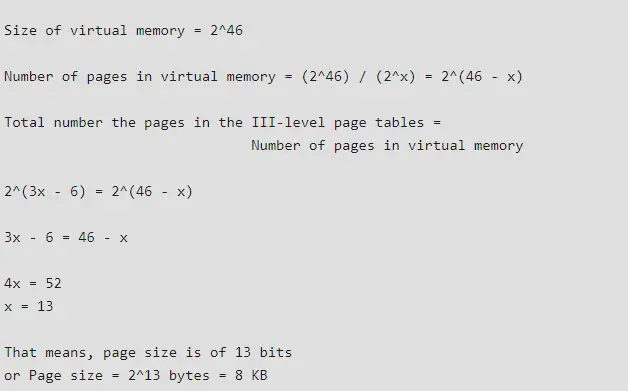

Q. 52 A computer uses 46-bit virtual address, 32-bit physical address, and a three-level paged page table organization. The page table base register stores the base address of the

first-level table ^T1h, which occupies exactly one page. Each entry of T1 stores the base

address of a page of the second-level table ^T2h. Each entry of T2 stores the base address

of a pae of the third-level table ^T3h. Each entry of T3 stores a page table entry (PTE).

The PTE is 32 bits in size. The processor used in the computer has a 1MB 16-way set

associative virtually indexed physically tagged cache. The cache block size is 64 bytes.

What is the size of a page in KB in this computer?

(A) 2

(B) 4

(C) 8

(D) 16

Answer: (C)

Explanation: