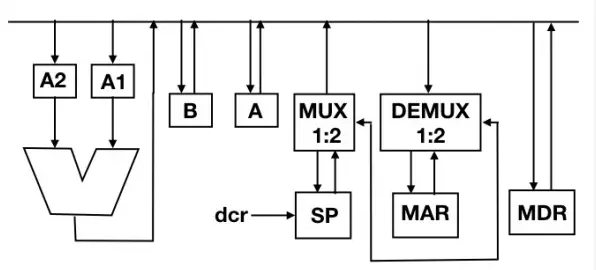

Q. 38 Consider the following data path of a simple non-pilelined CPU. The registers A, B, A1, A2, MDR, the bus and the ALU are 8-bit wide. SP and MAR are 16-bit registers. The MUX is of size 8 × (2:1) and the DEMUX is of size 8 × (1:2). Each memory operation takes 2 CPU clock cycles and uses MAR (Memory Address Register) and MDR (Memory Date Register). SP can be decremented locally.

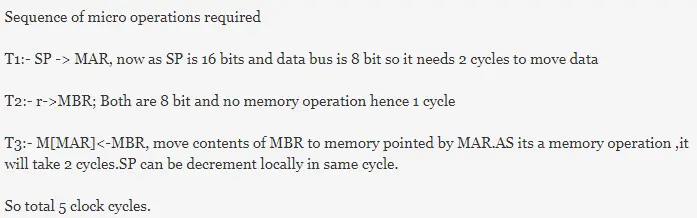

The CPU instruction “push r” where, r=r= AA or BB has the specification

M[SP]←rM[SP]←r SP←SP−1

How many CPU clock cycles are needed to execute the “push r” instruction?

(A) 2

(B) 3

(C) 4

(D) 5

Answer: (D)

Explanation: