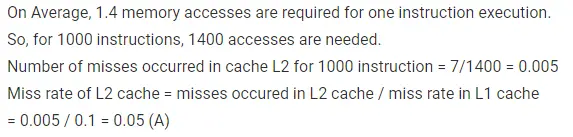

Q. 24 Consider a two-level cache hierarchy L1 and L2 caches. An application incurs 1.4 memory accesses per instruction on average. For this application, the miss rate of L1 cache 0.1, the L2 cache experience on average. 7 misses per 1000 instructions. The miss rate of L2 expressed correct to two decimal places is ______________.

Note: This questions appeared as Numerical Answer Type.

(A) 0.05

(B) 0.06

(C) 0.07

(D) 0.08

Answer: (A)

Explanation: